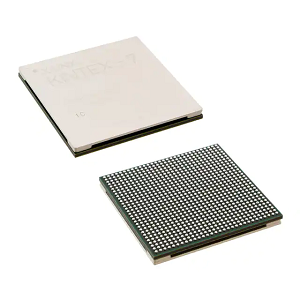

XC7K420T-2FFG901I - Araeau Giât Rhaglenadwy Maes Cylchedau Integredig, Mewnblanedig, Rhaglenadwy

Nodweddion Cynnyrch

| MATH | ARLUNIO |

| Categori | Cylchedau Integredig (ICs)Gwreiddio Araeau Gatiau Rhaglenadwy Maes (FPGAs) |

| gwneuthurwr | AMD |

| cyfres | Kintex®-7 |

| lapio | hambwrdd |

| Statws cynnyrch | Actif |

| Mae DigiKey yn rhaglenadwy | Heb ei wirio |

| Rhif LAB/CLB | 32575 |

| Nifer o elfennau/unedau rhesymeg | 416960 |

| Cyfanswm nifer y darnau RAM | 30781440 |

| Nifer yr I/O | 380 |

| Foltedd - Cyflenwad pŵer | 0.97V ~ 1.03V |

| Math gosod | Math o gludiog arwyneb |

| Tymheredd gweithredu | -40 ° C ~ 100 ° C (TJ) |

| Pecyn/Tai | 900-BBGA, FCBGA |

| Amgáu cydran gwerthwr | 901-FCBGA (31x31) |

| Rhif meistr cynnyrch | XC7K420 |

| MATH | ARLUNIO |

| Categori | Cylchedau Integredig (ICs)Gwreiddio |

| gwneuthurwr | AMD |

| cyfres | Kintex®-7 |

| lapio | hambwrdd |

| Statws cynnyrch | Actif |

| Mae DigiKey yn rhaglenadwy | Heb ei wirio |

| Rhif LAB/CLB | 32575 |

| Nifer o elfennau/unedau rhesymeg | 416960 |

| Cyfanswm nifer y darnau RAM | 30781440 |

| Nifer yr I/O | 380 |

| Foltedd - Cyflenwad pŵer | 0.97V ~ 1.03V |

| Math gosod | Math o gludiog arwyneb |

| Tymheredd gweithredu | -40 ° C ~ 100 ° C (TJ) |

| Pecyn/Tai | 900-BBGA, FCBGA |

| Amgáu cydran gwerthwr | 901-FCBGA (31x31) |

| Rhif meistr cynnyrch | XC7K420 |

FPGAs

Manteision

Mae manteision FPGAs fel a ganlyn:

(1) Mae FPGAs yn cynnwys adnoddau caledwedd megis celloedd rhesymeg, RAM, lluosyddion, ac ati Trwy drefnu'r adnoddau caledwedd hyn yn rhesymegol, gellir gweithredu cylchedau caledwedd megis lluosyddion, cofrestrau, generaduron cyfeiriad, ac ati.

(2) Gellir dylunio FPGAs trwy ddefnyddio diagramau bloc neu Verilog HDL, o gylchedau giât syml i gylchedau FIR neu FFT.

(3) Gellir ail-raglennu FPGAs yn anfeidrol, gan lwytho datrysiad dylunio newydd mewn ychydig gannoedd o filieiliadau, gan ddefnyddio ad-drefnu i leihau gorbenion caledwedd.

(4) Mae amlder gweithredu'r FPGA yn cael ei bennu gan y sglodion FPGA yn ogystal â'r dyluniad, a gellir ei addasu neu ei ddisodli â sglodyn cyflymach i fodloni rhai gofynion heriol (er, wrth gwrs, nid yw'r amlder gweithredu yn ddiderfyn a gall cael ei gynyddu, ond yn cael ei reoli gan brosesau IC cyfredol a ffactorau eraill).

Anfanteision

Mae anfanteision FPGAs fel a ganlyn:

(1) Mae FPGAs yn dibynnu ar weithredu caledwedd ar gyfer pob swyddogaeth ac ni allant weithredu gweithrediadau fel neidiau amodol canghennog.

(2) Dim ond gweithrediadau pwynt sefydlog y gall FPGAs eu gweithredu.

I grynhoi: Mae FPGAs yn dibynnu ar galedwedd i weithredu'r holl swyddogaethau a gellir eu cymharu â sglodion pwrpasol o ran cyflymder, ond mae bwlch mawr mewn hyblygrwydd dylunio o'i gymharu â phroseswyr pwrpas cyffredinol.

Dylunio ieithoedd a llwyfannau

Mae dyfeisiau rhesymeg rhaglenadwy yn gludwyr caledwedd sy'n concriteiddio swyddogaethau sefydledig a manylebau technegol cymwysiadau electronig trwy dechnoleg EDA.Mae FPGAs, fel un o'r dyfeisiau prif ffrwd sy'n gweithredu'r llwybr hwn, yn canolbwyntio'n uniongyrchol ar ddefnyddwyr, yn hynod hyblyg ac amlbwrpas, yn hawdd eu defnyddio, ac yn gyflym i'w profi a'u gweithredu mewn caledwedd.

Mae Iaith Disgrifiad Caledwedd (HDL) yn iaith a ddefnyddir i ddylunio systemau rhesymeg digidol a disgrifio cylchedau digidol, a'r prif rai a ddefnyddir yn gyffredin yw VHDL, Verilog HDL, System Verilog a System C.

Fel iaith ddisgrifio caledwedd gyffredinol, mae gan yr Iaith Disgrifiad Caledwedd Cylchred Integredig Cyflymder Uchel Iawn (VHDL) y nodweddion o fod yn annibynnol ar y gylched caledwedd benodol ac yn annibynnol ar y llwyfan dylunio, gyda manteision gallu disgrifio ystod eang, nid yn dibynnu ar ddyfeisiadau penodol, a'r gallu i ddisgrifio dyluniad rhesymeg rheoli cymhleth mewn cod trwyadl a chryno, ac ati Fe'i cefnogir gan lawer o gwmnïau EDA ac fe'i defnyddiwyd yn helaeth ym maes dylunio electronig.a ddefnyddir yn eang.

Mae VHDL yn iaith lefel uchel ar gyfer dylunio cylchedau, ac o'i chymharu ag ieithoedd disgrifio caledwedd eraill, mae ganddi nodweddion iaith syml, hyblygrwydd ac annibyniaeth o ddylunio dyfeisiau, gan ei gwneud yn iaith ddisgrifio caledwedd gyffredin ar gyfer technoleg EDA a gwneud technoleg EDA yn fwy. hygyrch i ddylunwyr.

Mae Verilog HDL yn iaith ddisgrifio caledwedd a ddefnyddir yn eang y gellir ei defnyddio mewn sawl cam o'r broses dylunio caledwedd, gan gynnwys modelu, synthesis ac efelychu.

Manteision Verilog HDL: tebyg i C, hawdd ei ddysgu a hyblyg.Achos-sensitif.Manteision ysgogi ysgrifennu a modelu.Anfanteision: ni ellir canfod llawer o wallau ar amser llunio.

Manteision VHDL: Cystrawen drylwyr, hierarchaeth glir.Anfanteision: amser ymgyfarwyddo hir, ddim yn ddigon hyblyg.

Mae meddalwedd Quartus_II yn amgylchedd dylunio aml-lwyfan cyflawn a ddatblygwyd gan Altera, a all ddiwallu anghenion dylunio amrywiol FPGAs a CPLDs, ac mae'n amgylchedd cynhwysfawr ar gyfer dylunio system rhaglenadwy ar sglodion.

Vivado Design Suite, amgylchedd dylunio integredig a ryddhawyd gan werthwr FPGA Xilinx yn 2012. Mae'n cynnwys amgylchedd dylunio integredig iawn a chenhedlaeth newydd o offer o lefel system i lefel IC, i gyd wedi'u hadeiladu ar fodel data graddadwy a rennir ac amgylchedd dadfygio cyffredin.mae Ystafell Ddylunio Xilinx Vivado yn darparu creiddiau IP FIFO y gellir eu cymhwyso'n hawdd i ddyluniadau.