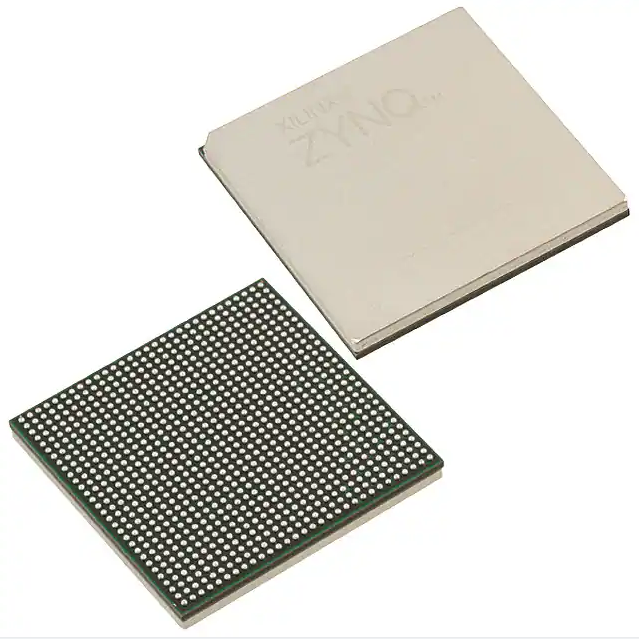

Cylched integredig XC5VFX30T-2FFG665I newydd a gwreiddiol

Nodweddion Cynnyrch

| MATH | DISGRIFIAD | DEWIS |

| Categori | Cylchedau Integredig (ICs) |

|

| Mfr | AMD Xilinx |

|

| Cyfres | Virtex®-5 FXT |

|

| Pecyn | Hambwrdd |

|

| Statws Cynnyrch | Actif |

|

| Nifer y LABs/CLBs | 2560 |

|

| Nifer yr Elfennau Rhesymeg/Celloedd | 32768. llarieidd-dra eg |

|

| Cyfanswm Darnau RAM | 2506752 |

|

| Nifer yr I/O | 360 |

|

| Foltedd - Cyflenwad | 0.95V ~ 1.05V |

|

| Math Mowntio | Mount Wyneb |

|

| Tymheredd Gweithredu | -40 ° C ~ 100 ° C (TJ) |

|

| Pecyn / Achos | 665-BBGA, FCBGA |

|

| Pecyn Dyfais Cyflenwr | 665-FCBGA (27×27) |

|

| Rhif Cynnyrch Sylfaenol | XC5VFX30 |

|

Adrodd Gwall Gwybodaeth Cynnyrch

Gweld Tebyg

Dogfennau a'r Cyfryngau

| MATH O ADNODDAU | CYSYLLTIAD |

| Taflenni data | Trosolwg Teulu Virtex-5 |

| Gwybodaeth Amgylcheddol | Xilinx REACH211 Cert |

| Dyluniad/Manyleb RhTC | Hysbysiad Di-blwm Traws-Llong 31/Hydref/2016 |

Dosbarthiadau Amgylcheddol ac Allforio

| NODWEDDIAD | DISGRIFIAD |

| Statws RoHS | Cydymffurfio â ROHS3 |

| Lefel Sensitifrwydd Lleithder (MSL) | 4 (72 Awr) |

| Statws REACH | REACH Heb ei effeithio |

| ECCN | 3A991D |

| HTSUS | 8542.39.0001 |

Arae giât rhaglenadwy maes

Aarae giât rhaglenadwy maes(FPGA) yn ancylched integredigwedi'i gynllunio i gael ei ffurfweddu gan gwsmer neu ddylunydd ar ôl gweithgynhyrchu - dyna pam y termmaes-rhaglenadwy.Yn gyffredinol, nodir cyfluniad FPGA gan ddefnyddio aiaith disgrifiad caledwedd(HDL), tebyg i'r hyn a ddefnyddir ar gyfer ancylched integredig cais-benodol(ASIC).Diagramau cylchedeu defnyddio o'r blaen i nodi'r ffurfweddiad, ond mae hyn yn fwyfwy prin oherwydd dyfodiadawtomeiddio dylunio electronigoffer.

Mae FPGAs yn cynnwys amrywiaeth orhaglenadwy blociau rhesymeg, a hierarchaeth o ryng-gysylltiadau y gellir eu hailgyflunio sy'n caniatáu i flociau gael eu gwifrau gyda'i gilydd.Gellir ffurfweddu blociau rhesymeg i berfformio cymhlethswyddogaethau cyfunol, neu weithredu mor symladwyon rhesymegfelACaXOR.Yn y rhan fwyaf o FPGAs, mae blociau rhesymeg hefyd yn cynnwyselfennau cof, a all fod yn symlfflip-fflopsneu flociau mwy cyflawn o gof.[1]Gellir ailraglennu llawer o FPGAs i weithredu gwahanolswyddogaethau rhesymeg, gan ganiatáu hyblygcyfrifiadura ailgyfluniofel y perfformiwyd ynmeddalwedd cyfrifiadurol.

Mae gan FPGAs rôl ryfeddol ynsystem wreiddiodatblygiad oherwydd eu gallu i ddechrau datblygu meddalwedd system ar yr un pryd â chaledwedd, galluogi efelychiadau perfformiad system ar gam cynnar iawn o'r datblygiad, a chaniatáu treialon system amrywiol ac iteriadau dylunio cyn cwblhau pensaernïaeth y system.[2]

Hanes[golygu]

Deilliodd y diwydiant FPGA ocof rhaglenadwy darllen yn unig(PROM) adyfeisiau rhesymeg rhaglenadwy(PLDs).Roedd gan PROMs a PLDs y dewis o gael eu rhaglennu mewn sypiau mewn ffatri neu yn y maes (rhaglenadwy maes).[3]

Alteraei sefydlu ym 1983 a chyflwynodd ddyfais resymeg ail-raglenadwy gyntaf y diwydiant ym 1984 - yr EP300 - a oedd yn cynnwys ffenestr cwarts yn y pecyn a oedd yn caniatáu i ddefnyddwyr ddisgleirio lamp uwch-fioled ar y dis i ddileu'rEPROMcelloedd a oedd yn dal cyfluniad y ddyfais.[4]

Xilinxcynhyrchu'r rhaglen gyntaf sy'n fasnachol hyfyw yn y maesarae porthyn 1985[3]– yr XC2064.[5]Roedd gan yr XC2064 gatiau rhaglenadwy a rhyng-gysylltiadau rhaglenadwy rhwng gatiau, dechreuadau technoleg a marchnad newydd.[6]Roedd gan yr XC2064 64 bloc rhesymeg ffurfweddadwy (CLBs), gyda dau fewnbwn tritablau chwilio(LUTs).[7]

Yn 1987, yCanolfan Rhyfela Arwyneb y Llyngesariannu arbrawf a gynigiwyd gan Steve Casselman i ddatblygu cyfrifiadur a fyddai'n gweithredu 600,000 o gatiau ail-raglennu.Roedd Casselman yn llwyddiannus a chyhoeddwyd patent yn ymwneud â'r system ym 1992.[3]

Parhaodd Altera a Xilinx heb eu herio a thyfodd yn gyflym o 1985 i ganol y 1990au pan eginodd cystadleuwyr, gan erydu cyfran sylweddol o'u cyfran o'r farchnad.Erbyn 1993, Actel (yn awrMicrosemi) yn gwasanaethu tua 18 y cant o'r farchnad.[6]

Roedd y 1990au yn gyfnod o dwf cyflym i FPGAs, o ran soffistigedigrwydd cylchedau a maint y cynhyrchiad.Yn y 1990au cynnar, defnyddiwyd FPGAs yn bennaf yntelathrebuarhwydweithio.Erbyn diwedd y degawd, daeth FPGAs i mewn i gymwysiadau defnyddwyr, modurol a diwydiannol.[8]

Erbyn 2013, roedd Altera (31 y cant), Actel (10 y cant) a Xilinx (36 y cant) gyda'i gilydd yn cynrychioli tua 77 y cant o farchnad FPGA.[9]

Mae cwmnïau fel Microsoft wedi dechrau defnyddio FPGAs i gyflymu systemau perfformiad uchel, cyfrifiadurol dwys (fel ycanolfannau datasy'n gweithredu euPeiriant chwilio Bing), oherwydd yperfformiad fesul watmantais darparu FPGAs.[10]Dechreuodd Microsoft ddefnyddio FPGAs icyflymuYn 2014, ac yn 2018 dechreuodd ddefnyddio FPGAs ar draws llwythi gwaith canolfannau data eraill ar gyfer euAsur cyfrifiadura cwmwlplatfform.[11]

Mae'r llinellau amser canlynol yn nodi cynnydd mewn gwahanol agweddau ar ddyluniad FPGA:

Gatiau

- 1987: 9,000 o gatiau, Xilinx[6]

- 1992: 600,000, Adran Rhyfela Arwyneb y Llynges[3]

- 2000au cynnar: miliynau[8]

- 2013: 50 miliwn, Xilinx[12]

Maint y farchnad

- 1985: FPGA masnachol cyntaf : Xilinx XC2064[5][6]

- 1987: $14 miliwn[6]

- c.1993: >$385 miliwn[6][dilysu wedi methu]

- 2005: $1.9 biliwn[13]

- Amcangyfrifon 2010: $2.75 biliwn[13]

- 2013: $5.4 biliwn[14]

- Amcangyfrif 2020: $9.8 biliwn[14]

Dylunio yn dechrau

Adechrau dylunioyn ddyluniad arferol newydd i'w weithredu ar FPGA.

Dyluniad[golygu]

Mae gan FPGAs cyfoes adnoddau mawr oadwyon rhesymega blociau RAM i weithredu cyfrifiannau digidol cymhleth.Gan fod dyluniadau FPGA yn defnyddio cyfraddau I/O cyflym iawn a data deugyfeiriadolbysus, mae'n dod yn her i wirio amseriad cywir o ddata dilys o fewn amser gosod a dal amser.

Cynllunio llawrgalluogi dyrannu adnoddau o fewn FPGAs i fodloni'r cyfyngiadau amser hyn.Gellir defnyddio FPGAs i weithredu unrhyw swyddogaeth resymegol aASICyn gallu perfformio.Y gallu i ddiweddaru'r swyddogaeth ar ôl ei anfon,ail-gyflunio rhannolo ran o'r dyluniad[17]ac mae'r costau peirianneg anghylchol isel o'u cymharu â dyluniad ASIC (er gwaethaf y gost uned gyffredinol uwch), yn cynnig manteision i lawer o gymwysiadau.[1]

Mae gan rai FPGAs nodweddion analog yn ogystal â swyddogaethau digidol.Y nodwedd analog fwyaf cyffredin yw rhaglenadwycyfradd lladdar bob pin allbwn, gan ganiatáu i'r peiriannydd osod cyfraddau isel ar binnau wedi'u llwytho'n ysgafn a fyddai fel arallmodrwyneucwplyn annerbyniol, ac i osod cyfraddau uwch ar binnau wedi'u llwytho'n drwm ar sianeli cyflym a fyddai fel arall yn rhedeg yn rhy araf.[18][19]Hefyd yn gyffredin mae cwarts-oscillators grisial, ar-sglodion ymwrthedd-cynhwysedd oscillators, adolenni wedi'u cloi fesul camgyda gwreiddioOsgiliaduron a reolir gan foltedda ddefnyddir ar gyfer cynhyrchu a rheoli cloc yn ogystal ag ar gyfer cyflymder uchel serializer-deserializer (SERDES) trawsyrru clociau ac adfer cloc derbynnydd.Gweddol gyffredin yn wahaniaetholcymaryddionar binnau mewnbwn sydd wedi'u cynllunio i fod yn gysylltiedig â nhwsignalau gwahaniaetholsianeli.Ychydig o “signal cymysgMae gan FPGAs” ymylol integredigtrawsnewidyddion analog-i-ddigidol(ADCs) atrawsnewidwyr digidol-i-analog(DACs) gyda blociau cyflyru signal analog sy'n caniatáu iddynt weithredu fel asystem-ar-a-sglodyn(SoC).[20]Mae dyfeisiau o'r fath yn cymylu'r llinell rhwng FPGA, sy'n cario rhai digidol a sero ar ei ffabrig rhyng-gysylltu rhaglenadwy mewnol, aarae analog rhaglenadwy maes(FPAA), sy'n cario gwerthoedd analog ar ei ffabrig rhyng-gysylltu rhaglenadwy mewnol.