Stoc IC gwreiddiol gwirioneddol newydd sbon Cydrannau Electronig Cymorth Sglodion Ic Gwasanaeth BOM TPS62130AQRGTRQ1

Nodweddion Cynnyrch

| MATH | DISGRIFIAD |

| Categori | Cylchedau Integredig (ICs) |

| Mfr | Offerynnau Texas |

| Cyfres | Modurol, AEC-Q100, DCS-Control™ |

| Pecyn | Tâp a Rîl (TR) Tâp Torri (CT) Digi-Reel® |

| SPQ | 250T&R |

| Statws Cynnyrch | Actif |

| Swyddogaeth | Cam i Lawr |

| Ffurfweddiad Allbwn | Cadarnhaol |

| Topoleg | Buck |

| Math o Allbwn | Addasadwy |

| Nifer yr Allbynnau | 1 |

| Foltedd - Mewnbwn (Isafswm) | 3V |

| Foltedd - Mewnbwn (Uchafswm) | 17V |

| Foltedd - Allbwn (Isafswm / Sefydlog) | 0.9V |

| Foltedd - Allbwn (Uchafswm) | 6V |

| Cyfredol - Allbwn | 3A |

| Amlder - Newid | 2.5MHz |

| Rectifier Cydamserol | Oes |

| Tymheredd Gweithredu | -40°C ~ 125°C (TJ) |

| Math Mowntio | Mount Wyneb |

| Pecyn / Achos | Pad Agored 16-VFQFN |

| Pecyn Dyfais Cyflenwr | 16-VQFN (3x3) |

| Rhif Cynnyrch Sylfaenol | TPS62130 |

1.

Unwaith y byddwn yn gwybod sut mae'r IC wedi'i adeiladu, mae'n bryd esbonio sut i'w wneud.I wneud llun manwl gyda chan chwistrellu o baent, mae angen i ni dorri mwgwd ar gyfer y llun a'i roi ar bapur.Yna rydyn ni'n chwistrellu'r paent yn gyfartal ar y papur ac yn tynnu'r mwgwd pan fydd y paent wedi sychu.Mae hyn yn cael ei ailadrodd dro ar ôl tro i greu patrwm taclus a chymhleth.Fe'm gwneir yn yr un modd, trwy bentyrru haenau ar ben ei gilydd mewn proses guddio.

Gellir rhannu'r broses o gynhyrchu ICs yn 4 cam syml.Er y gall y camau gweithgynhyrchu gwirioneddol amrywio a gall y deunyddiau a ddefnyddir fod yn wahanol, mae'r egwyddor gyffredinol yn debyg.Mae'r broses ychydig yn wahanol i beintio, sef bod ICs yn cael eu cynhyrchu â phaent ac yna'n cael eu cuddio, tra bod paent yn cael ei guddio yn gyntaf ac yna'n cael ei beintio.Disgrifir pob proses isod.

Sputtering metel: Mae'r deunydd metel sydd i'w ddefnyddio wedi'i ysgeintio'n gyfartal ar y wafer i ffurfio ffilm denau.

Cais ffotoresist: Mae'r deunydd ffotoresist yn cael ei roi yn gyntaf ar y wafer, a thrwy'r mwgwd ffoto (bydd egwyddor y mwgwd ffoto yn cael ei esbonio y tro nesaf), mae'r trawst golau yn cael ei daro ar y rhan ddiangen i ddinistrio strwythur y deunydd ffotoresist.Yna caiff y deunydd sydd wedi'i ddifrodi ei olchi i ffwrdd â chemegau.

Ysgythriad: Mae'r wafer silicon, nad yw'n cael ei warchod gan y ffotoresydd, wedi'i ysgythru â thrawst ïon.

Tynnu ffotoresist: Mae'r ffotoresist sy'n weddill yn cael ei ddiddymu gan ddefnyddio datrysiad tynnu ffotoresist, gan gwblhau'r broses.

Y canlyniad terfynol yw sawl sglodion 6IC ar un wafer, sydd wedyn yn cael eu torri allan a'u hanfon i'r ffatri becynnu i'w pecynnu.

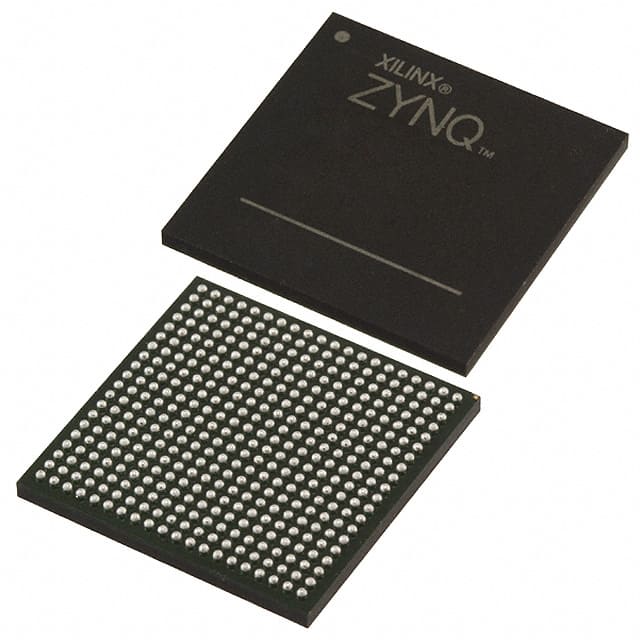

2.Beth yw'r broses nanomedr?

Mae Samsung a TSMC yn ei frwydro yn y broses lled-ddargludyddion datblygedig, pob un yn ceisio cael y blaen yn y ffowndri i sicrhau archebion, ac mae bron wedi dod yn frwydr rhwng 14nm a 16nm.A beth yw'r manteision a'r problemau a ddaw yn sgil y broses lai?Isod byddwn yn esbonio'r broses nanomedr yn fyr.

Pa mor fach yw nanometr?

Cyn i ni ddechrau, mae'n bwysig deall beth mae nanometrau yn ei olygu.Mewn termau mathemategol, mae nanomedr yn 0.000000001 metr, ond mae hon yn enghraifft eithaf gwael - wedi'r cyfan, dim ond sawl sero y gallwn eu gweld ar ôl y pwynt degol ond nid oes gennym unrhyw synnwyr gwirioneddol o'r hyn ydyn nhw.Os byddwn yn cymharu hyn â thrwch ewin, gallai fod yn fwy amlwg.

Os ydym yn defnyddio pren mesur i fesur trwch hoelen, gallwn weld bod trwch hoelen tua 0.0001 metr (0.1 mm), sy'n golygu, os ydym yn ceisio torri ochr hoelen yn 100,000 o linellau, pob llinell yn cyfateb i tua 1 nanometr.

Unwaith y byddwn yn gwybod pa mor fach yw nanomedr, mae angen inni ddeall pwrpas crebachu'r broses.Prif bwrpas crebachu'r grisial yw ffitio mwy o grisialau i sglodyn llai fel na fydd y sglodion yn dod yn fwy oherwydd datblygiad technolegol.Yn olaf, bydd maint llai y sglodyn yn ei gwneud hi'n haws ffitio i mewn i ddyfeisiau symudol a bodloni'r galw yn y dyfodol am denau.

Gan gymryd 14nm fel enghraifft, mae'r broses yn cyfeirio at y maint gwifren lleiaf posibl o 14nm mewn sglodion.